Thus, the device can pipeline its accesses through coherent accesses and deliver better throughput.ĬXL.memory allows a host processor or other CXL devices to access memory attached to a CXL device. If the SmartNIC implementing PGAS was a PCIe device, it had to wait for a read request to complete before launching a subsequent write on the PCIe Link since writes in PCIe are in a different flow-control class and can bypass prior reads.Ĭaching enables the device to prefetch the ownership of the cache line to be written while it requests the read data it doesn’t have to wait for the write to be flushed to the system memory since completing the write in the local cache ensures architectural global visibility. Ordering semantics of such mechanisms can be performed efficiently with cache coherency by the device. Once a device caches a memory location, it can implement any advanced semantics since it’s guaranteed to be performed atomically within the 64-byte cache line boundary.Īnother example is networking devices implementing advanced inter-process communication mechanisms such as partitioned global address space (PGAS). 3).Ĭaching also enables efficient implementation of complex semantics such as advanced atomics and advanced telemetry used by devices like SmartNICs. This is useful for CXL accelerators represented as Type-1 and Type-2 CXL devices (Fig. It’s much more efficient than the ~500-ns access latency and ~50-GB/s bandwidth in accessing a memory location across a non-cached interconnect. Caches provide low-latency (~10-ns access latency) and high-bandwidth (~150 GB/s) accesses if the location is cached by the device. The device can cache only the data that it needs. That’s due to the efficiency of moving only the needed data and moving it only once. However, where the data access has either spatial or temporal locality (i.e., the same data is repeatedly accessed and/or where accesses are to sequentially increasing addresses), or in cases where the data access is sparse (i.e., a small percentage of the data is really accessed), caching semantics helps tremendously. PCIe devices transfer data and flag across the PCIe Link(s) using the load-store I/O protocol while enforcing the producer-consumer ordering model for data consistency. Additional details can be found in the references (see References at the end of the article). In this article, we delve into some details of CXL 1.0 and CXL 1.1 specification and usage models.

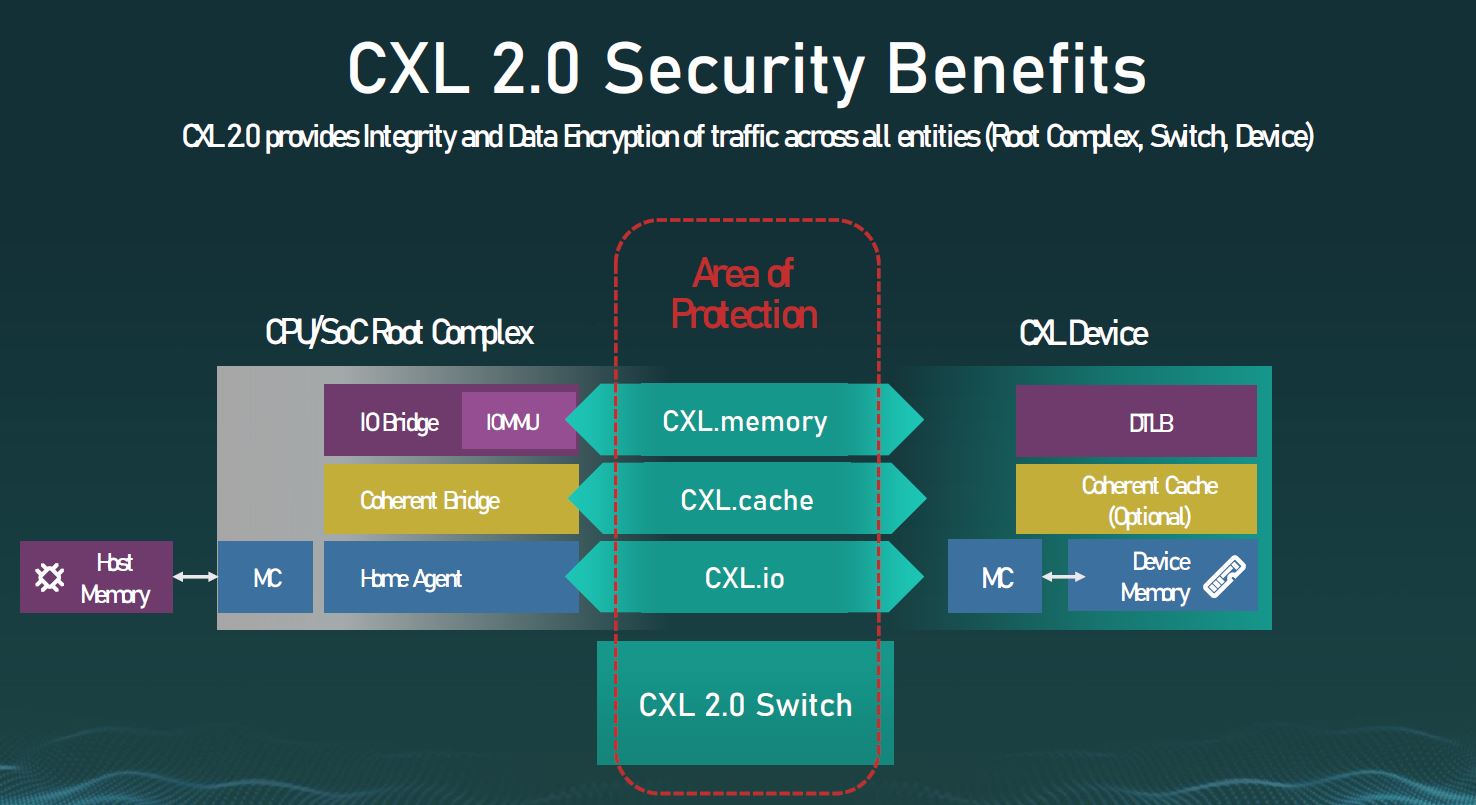

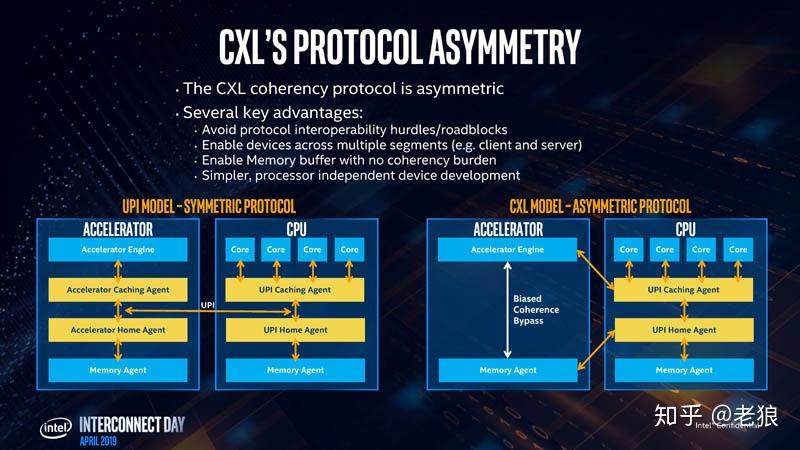

Moreover, since the CPU is primarily responsible for coherency management, it can reduce device cost and complexity as well as overhead traditionally associated with coherency management across an I/O link. Thus, both the CPU and CXL device can share resources for higher performance and reduced software stack complexity. It maintains a unified, coherent memory space between the CPU (host processor) and any memory on the attached CXL device. Coherency and memory semantics in a heterogeneous environment are increasingly important as processing data in such emerging applications requires a diverse mix of scalar, vector, matrix, and spatial architectures deployed in CPUs, GPUs, FPGAs, SmartNICs, and other accelerators.ĬXL achieves these objectives by supporting dynamic multiplexing between a rich set of protocols that includes I/O (CXL.io, which is based on PCIe), caching (CXL.cache), and memory (CXL.memory) semantics (Fig. 1).ĬXL is designed to address the growing needs of high-performance computational workloads by supporting heterogeneous processing and memory systems with applications in artificial intelligence (AI), machine learning (ML), communication systems, and high-performance computing (HPC).

CXL is based on the PCI Express (PCIe) 5.0 physical-layer infrastructure with plug-and-play interoperability between PCIe and CXL devices on a PCIe slot (Fig. The Compute Express Link (CXL) is an open industry-standard interconnect offering coherency and memory semantics using high-bandwidth and low-latency connectivity between host processor and devices such as accelerators, memory buffers, and smart I/O devices.

0 Comments

Leave a Reply. |

Details

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed